Zynq-based WISER platform - Building the Firmware

Table of Contents

- SDR Tutorials

Description

This tutorial is a quick guide for building the WISER Zynq-based firmware.

Getting the FPGA source code

- If using a Windows machine, create a folder D:/Repository/crkit_svn

- Checkout the source code from the SVN repository http://crkit.orbit-lab.org/svn/crkit

- crkit_svn/design/trunk/vivado_build/crkit_spec_sense.zip is the spectrum sensing application build. Uncompress the zip file to D:/hw/crkit_zd folder.

Building the FPGA design

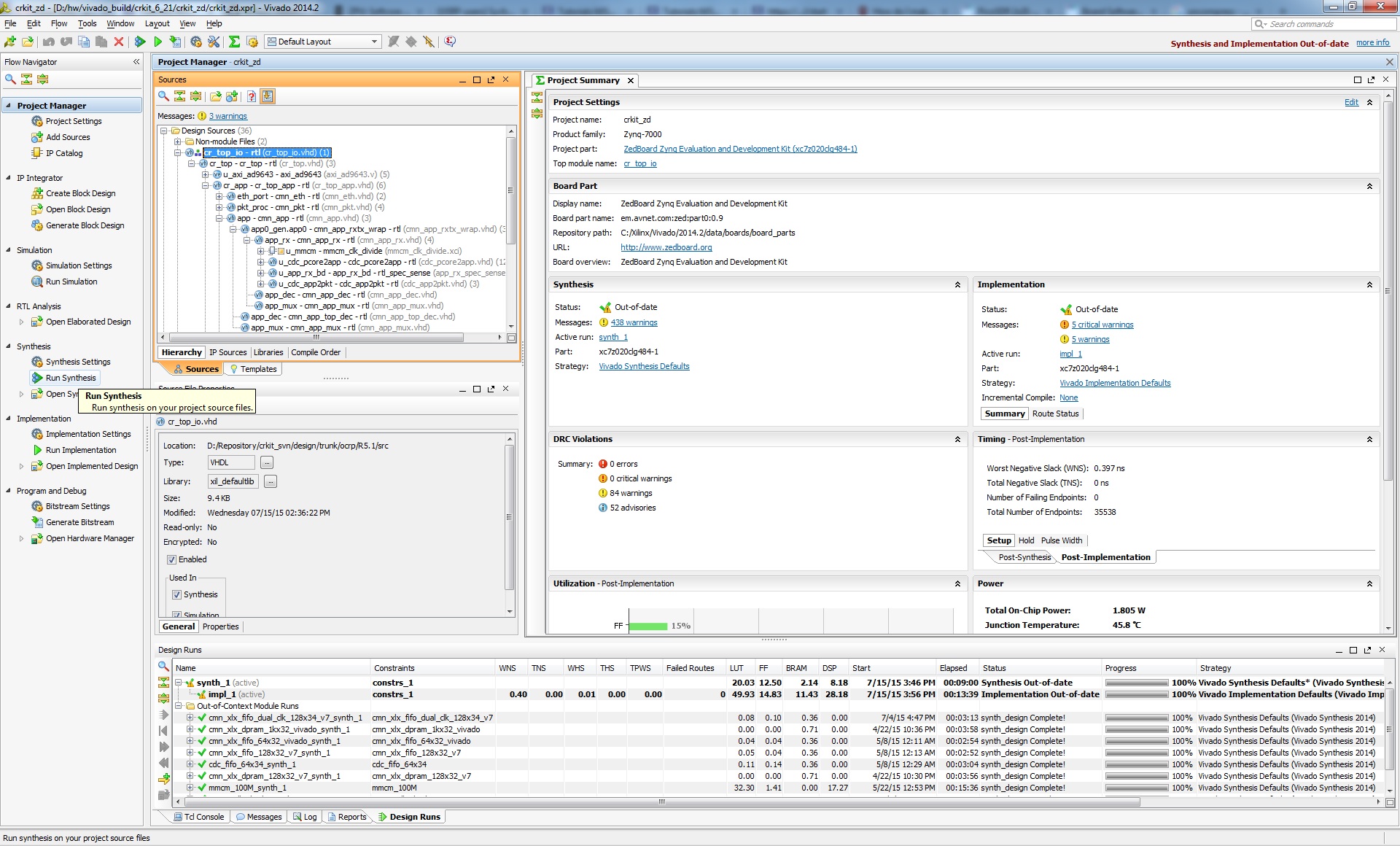

- Open crkit_zd.xpr, the Vivado project. The FPGA design consists of the CRKIT framework and the spectrum sensing receive application (instantiated as u_app_rx_bd). All the files here, point to the source files in the repository D:/Repository/crkit_svn. In case the source files are located elsewhere, they will have to be added to the project.

- Edit the code as needed, synthesize, implement and generate the bit stream.

Building ARM core software

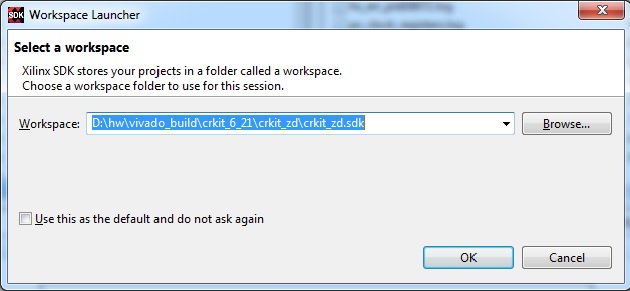

- Launch Xilinx SDK and select the crkit_zd workspace from the above project

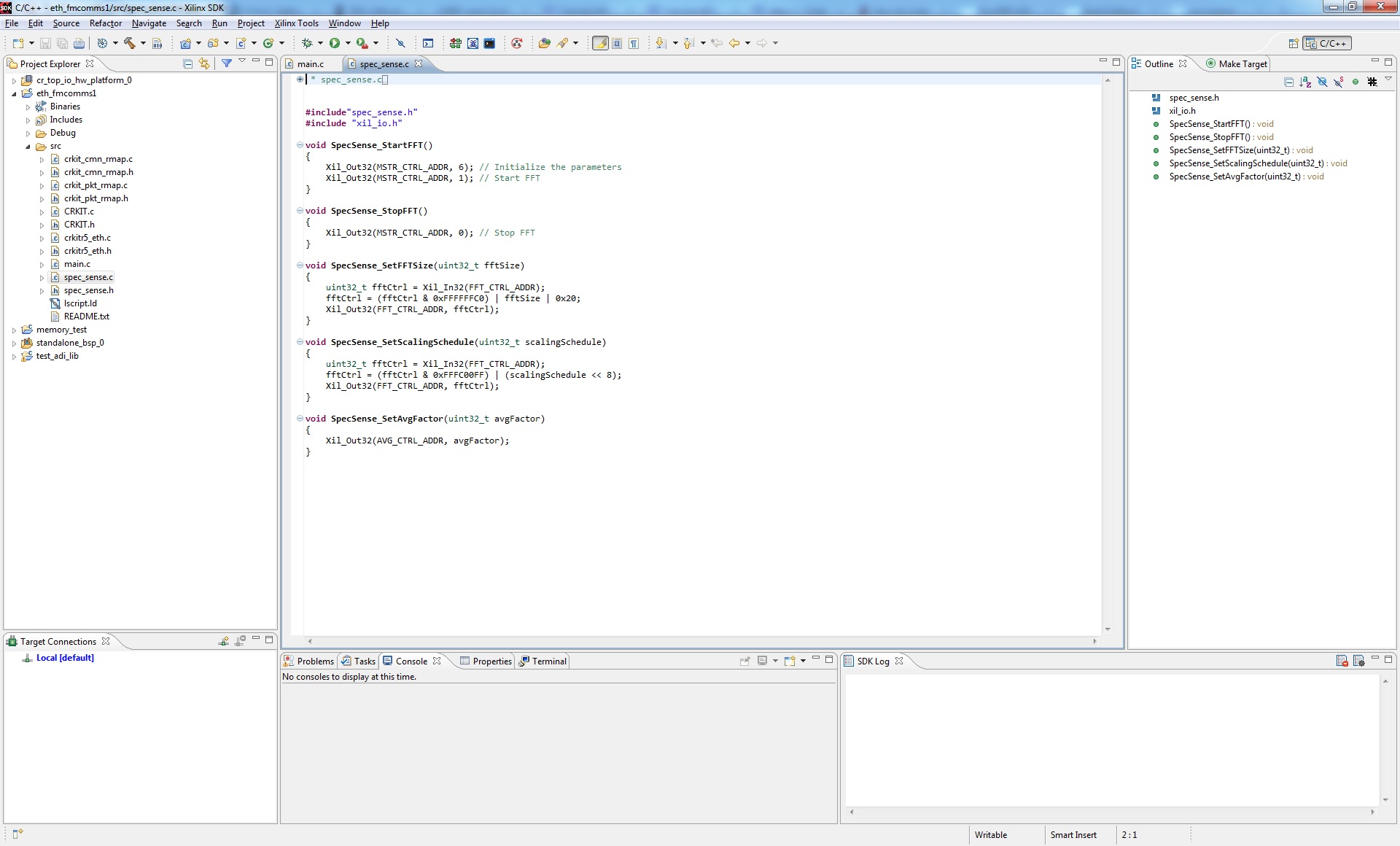

- The workspace has the imported hardware platform, a board support package and 3 projects

- memory_test - A memory test application to test the memory ranges in the hardware design.

- test_adi_lib - library of no-OS drivers for the RF card - ADFMCOMMS1.

- ethfmcomms1 - the spectrum sensing software which sets up and controls the framework, the RF front end (using test_adi_lib), and the spectrum sensing application.

- Edit the source and obtain .elf file by building the project.

Last modified

11 years ago

Last modified on Sep 24, 2015, 6:50:57 PM

Attachments (3)

- vivado_project.jpg (638.5 KB ) - added by 11 years ago.

- sdk_workspace.jpg (286.7 KB ) - added by 11 years ago.

- sdk_workspace_launcher.jpg (43.8 KB ) - added by 11 years ago.

Download all attachments as: .zip

Note:

See TracWiki

for help on using the wiki.